| <b>Document Title</b>      | Guide to BSW Distribution |

|----------------------------|---------------------------|

| Document Owner             | AUTOSAR                   |

| Document Responsibility    | AUTOSAR                   |

| Document Identification No | 631                       |

| Document Status          | published        |

|--------------------------|------------------|

| Part of AUTOSAR Standard | Classic Platform |

| Part of Standard Release | R21-11           |

| Document Change History |         |                                  |                                                                                                                                                         |  |  |

|-------------------------|---------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                    | Release | Changed by                       | Description                                                                                                                                             |  |  |

| 2021-11-25              | R21-11  | AUTOSAR<br>Release<br>Management | <ul> <li>Clarified partition scope of MCAL</li> <li>Removed restriction for BSW partitions per core</li> </ul>                                          |  |  |

| 2020-11-30              | R20-11  | AUTOSAR<br>Release<br>Management | Added chapter on crypto-stack distribution                                                                                                              |  |  |

| 2019-11-28              | R19-11  | AUTOSAR<br>Release<br>Management | <ul> <li>Incorporation of concept "BSW Multicore Distribution"</li> <li>Changed Document Status from Final to published</li> </ul>                      |  |  |

| 2018-10-31              | 4.4.0   | AUTOSAR<br>Release<br>Management | Incorporation of concept "MCAL Multicore Distribution"                                                                                                  |  |  |

| 2017-12-08              | 4.3.1   | AUTOSAR<br>Release<br>Management | Editorial changes                                                                                                                                       |  |  |

| 2016-11-30              | 4.3.0   | AUTOSAR<br>Release<br>Management | Editorial changes                                                                                                                                       |  |  |

| 2014-10-31              | 4.2.1   | AUTOSAR<br>Release<br>Management | <ul> <li>Incorporation of concept         "Mechanisms and constraints to protect ASIL BSW against QM BSW"     </li> <li>Minor clarifications</li> </ul> |  |  |

| 2014-03-31              | 4.1.3   | AUTOSAR<br>Release<br>Management | Clarified terms                                                                                                                                         |  |  |

| 2013-03-15 | 4.1.1 | AUTOSAR<br>Administration | Initial release |

|------------|-------|---------------------------|-----------------|

|            |       | Administration            |                 |

#### **Disclaimer**

This work (specification and/or software implementation) and the material contained in it, as released by AUTOSAR, is for the purpose of information only. AUTOSAR and the companies that have contributed to it shall not be liable for any use of the work.

The material contained in this work is protected by copyright and other types of intellectual property rights. The commercial exploitation of the material contained in this work requires a license to such intellectual property rights.

This work may be utilized or reproduced without any modification, in any form or by any means, for informational purposes only. For any other purpose, no part of the work may be utilized or reproduced, in any form or by any means, without permission in writing from the publisher.

The work has been developed for automotive applications only. It has neither been developed, nor tested for non-automotive applications.

The word AUTOSAR and the AUTOSAR logo are registered trademarks.

# **Table of Contents**

| 1 | Introduction |                |                                                             |    |  |

|---|--------------|----------------|-------------------------------------------------------------|----|--|

| 2 | BSV          | V Distribution | on in Multi-Core Systems                                    | 7  |  |

|   | 2.1          | Overviev       | v                                                           | 7  |  |

|   |              | 2.1.1          | Supported Scenarios                                         | 7  |  |

|   |              | 2.1.2          | Performance Use Cases and Hardware Assigned to Different    |    |  |

|   |              |                | Cores                                                       | 8  |  |

|   |              | 2.1.3          | Technical Overview                                          | 8  |  |

|   | 2.2          |                | Execution of BSW modules                                    | 11 |  |

|   |              | 2.2.1          | Core-Dependent Branching                                    | 11 |  |

|   |              | 2.2.2          | Master/Satellite-approach                                   | 11 |  |

|   |              | 2.2.3          | Using the BSW Scheduler for Inter-Partition-Communication   | 13 |  |

|   |              | 2.2.4          | Using Shared Buffers (in systems without memory protection) | 14 |  |

|   |              | 2.2.5          | Accessing Hardware/Drivers                                  | 16 |  |

|   |              | 2.2.6          | Concurrency safe implementation of modules                  | 16 |  |

|   |              | 2.2.7          | Kernel based Master-Satellite Realization                   | 17 |  |

|   |              | 2.2.8          | Atomic Operations Library                                   | 20 |  |

|   | 2.3          |                | terfaces for Parallel BSW execution                         | 20 |  |

|   | 2.4          |                | ation of Basic Software in Partitioned Systems              | 21 |  |

|   |              | 2.4.1          | Task Mapping                                                | 21 |  |

|   |              | 2.4.2          | General Configuration of Master and Satellites              | 25 |  |

|   |              | 2.4.3          | Configuring the BswM (per Partition)                        | 25 |  |

|   |              | 2.4.4          | Configuring the EcuM (per Core)                             | 26 |  |

|   | 2.5          |                | istribution                                                 | 27 |  |

|   |              | 2.5.1          | Introduction                                                | 27 |  |

|   |              | 2.5.2          | Assumptions of Use                                          | 27 |  |

|   |              | 2.5.3          | Constraints                                                 | 28 |  |

|   |              | 2.5.4          | Definition of MCAL Users                                    | 28 |  |

|   |              | 2.5.5          | Multiple Partitions versus Multi-Core MCAL                  | 29 |  |

|   |              | 2.5.6          | Multi-Core Capabilities Classification Criteria             | 30 |  |

|   |              | 2.5.7          | Definition of MCAL Multi-Core Types                         | 31 |  |

|   |              | 2.5.8          | Mapping MCAL Modules to Multi-Core Types                    | 35 |  |

|   |              | 2.5.9          | Seperation Stragies and Mapping of Elements                 | 37 |  |

|   |              | 2.5.10         | Separation Strategies                                       | 38 |  |

|   |              | 2.5.11         | Mapping of Elements                                         | 40 |  |

|   |              | 2.5.12         | Examples                                                    | 44 |  |

|   | 2.6          |                | Software to different Core Partitions                       | 45 |  |

|   |              | 2.6.1          | Allocation with Global scope                                | 45 |  |

|   |              | 2.6.2          | Allocation with Local scope                                 | 46 |  |

|   |              | 2.6.3          | Allocation using Cloning capabilities                       | 47 |  |

|   |              | 2.6.4          | How to determine the Core Scope?                            | 48 |  |

|   | 2.7          | _              | ack Distribution                                            | 52 |  |

|   |              | 2.7.1          | Introduction                                                | 52 |  |

|   |              | 2.7.2          | Assumptions of Use                                          | 53 |  |

|   |              |                |                                                             |    |  |

# Guide to BSW Distribution AUTOSAR CP R21-11

|   |       | 2.7.3          | Constraints                        | 53       |

|---|-------|----------------|------------------------------------|----------|

|   |       | 2.7.4          | Functional Elements                | 54       |

|   |       | 2.7.5          | Architectural Components           | 57       |

|   | 2.8   | Crypto-S       | Stack Distribution                 | 59       |

|   |       | 2.8.1          | Freshness value handling           | 60       |

| 3 | BSW   | / Distribution | on in Safety Systems               | 61       |

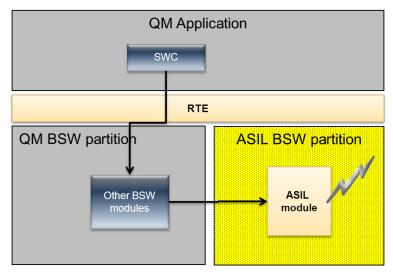

|   | 3.1   | General        | overview on safety                 | 31       |

|   | 3.2   | Safety so      | olutions in AUTOSAR                | 31       |

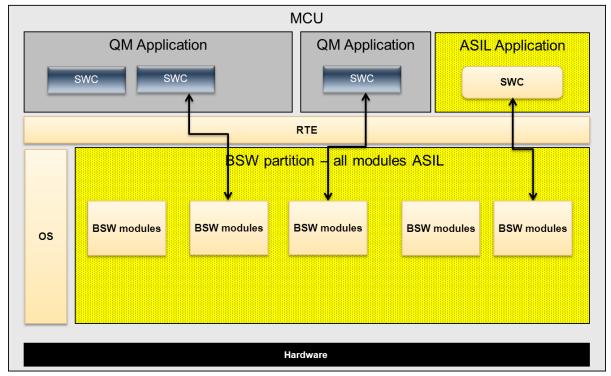

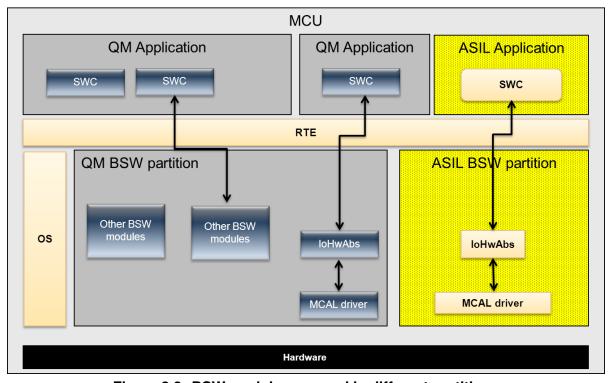

|   |       | 3.2.1          | Some modules are always ASIL       | 64       |

|   |       | 3.2.2          | Overall configuration              | 64       |

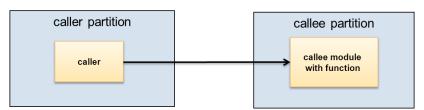

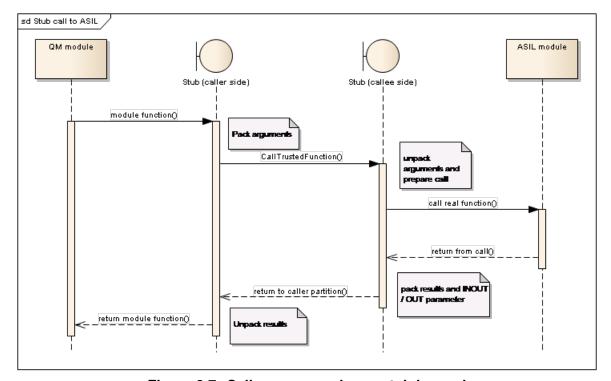

|   |       | 3.2.3          | Crossing partition boundaries      | 66       |

|   |       | 3.2.4          | Access to peripherals / hardware   | 74       |

|   |       | 3.2.5          | Startup, Shutdown and Sleep/Wakeup | 76       |

|   |       | 3.2.6          |                                    | 78       |

|   |       | 3.2.7          | 9 P                                | 78       |

|   |       | 3.2.8          | <b>9 9</b>                         | 79       |

|   |       | 3.2.9          |                                    | 79       |

|   |       | 3.2.10         | Constraints                        | 30       |

| 4 | Outlo | ook on Upo     | coming AUTOSAR Versions 8          | 32       |

|   | 4.1   | Known li       | mitations                          | 32       |

|   | 4.2   |                |                                    | 32       |

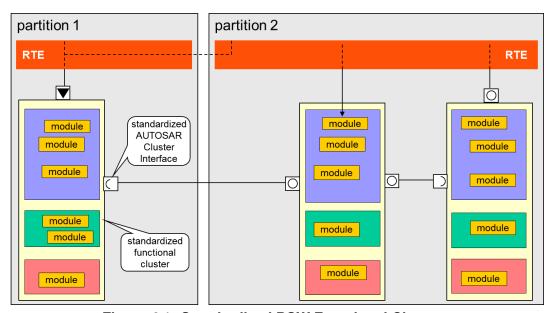

|   | 4.3   | Standard       | dized BSW functional clusters 8    | 32       |

| 5 | Glos  | sary           | 8                                  | 34       |

|   | 5.1   | Acronym        | ns and abbreviations               | 34       |

|   | 5.2   |                |                                    | 34<br>34 |

| 6 |       |                |                                    | 36       |

| U | neie  | rences         |                                    | סכ       |

# 1 Introduction

This document is a general introduction to the distribution of BSW in AUTOSAR systems. It consists of two parts, one focusing on the distribution of BSW in case of multi-core and the other focusing on distribution in case of safety.

chapter 2 guides to the development and configuration of AUTOSAR-compliant software for multi-core systems. As of release 4.1, it addresses the allocation of AUTOSAR BSW modules [1] to partitions on multi-core systems and their interaction only. The allocation of BSW modules to different BSW partitions allows for both enhanced functional safety and increased performance.

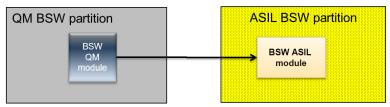

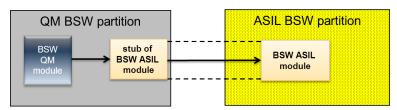

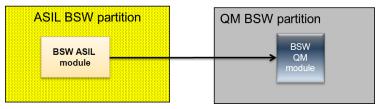

In chapter 3 the BSW distribution in safety cases is described. As of release 4.2 AUTOSAR allows to map BSW modules into different partitions and to protect those partitions against each other.

chapter 4 gives an outlook of possible future extensions in the area of BSW distribution.

A glossary of technical terms and a list of references to external information are provided in chapter 5 and chapter 6.

# 2 BSW Distribution in Multi-Core Systems

# 2.1 Overview

This chapter contains a description of the supported scenarios for distributed execution of BSW modules on several partitions and cores and a number of use cases in which a distribution of the BSW can enhance performance. It also introduces basic synchronization concepts applicable to distributed BSW execution, and an introduction to inter-partition communication.

# 2.1.1 Supported Scenarios

It is possible to assign functional clusters of BSW modules ("BSW Functional cluster"), which are used by applications to access buses, non-volatile memory, I/O channels, and watchdogs, to different BSW partitions for safety or performance reasons. The clustering of BSW modules is currently not standardized. Except for the MCAL, parallel usage of the same type of functional clusters in different partitions ("duplication") is not generally supported, but it is possible by using a master satellite approach. Functional clusters to partitions may be assigned such that

- a BSW functional cluster is only available in one partition

- a BSW functional cluster is available on all partitions with all interfaces

- a BSW functional cluster is distributed over multiple partitions, possibly with partition specific subsets of functionality, to allow a high grade of concurrency.

By supporting the scenarios listed above, AUTOSAR addresses the following essential features:

- All code for communication between BSW partitions can be generated for automatic adaptation to different system configurations. The cross partition communication mechanism can be generated with focus on efficiency, or, in future releases to help to provide freedom of interference.

- If access to system services (which are not part of a BSW functional cluster) is required, the according interfaces shall be provided to each BSW partition that needs the system service.

- Efficient access to HW abstraction and drivers is supported in each BSW partition.

In all scenarios, the communication between different module entities remains unchanged (in comparison to BSW running in a single partition).

# 2.1.2 Performance Use Cases and Hardware Assigned to Different Cores

The following use cases are examples for how system performance can be improved by allocation of the BSW to multiple partitions and cores, and how systems where the access to the peripheral hardware is assigned to multiple cores benefit from the allocation of the BSW to multiple partitions and cores.

- To increase system performance and to reduce resource consumption in systems that are distributed over several cores, it may be necessary to allocate functional clusters of BSW modules to different cores, e.g. communication modules on BSW partition "A" and I/O modules on BSW partition "B", depending on hardware architecture, load balancing and on distribution of SW-Cs. In particular, if HW resources are accessed exclusively by one core in a Multi-Core system, the performance is increased by locating the corresponding BSW users, services and drivers on that core.

- Signal gateway functionality is implemented by allocating a FlexRay cluster on one core and a CAN cluster on a different core. The two COM modules need to be synchronized in this case, and there must be some direct cross core communication between the two COM instances. One of the COM modules might be the master COM that coordinates the satellite COM on the other core.

- Two communication clusters are located on different cores, one accessing a CAN bus and the other one controlling a FlexRay bus. In case the application SW located above one of the communication clusters on the same core needs to send on both buses, the core local COM modules can directly communicate with their counterparts on the other core, to efficiently send the signal over either CAN or FlexRay. For received messages, COM has no information about receivers above the RTE. Therefore, COM has to forward the signals on the receiving side to the RTE, and the RTE is responsible for communication.

#### 2.1.3 Technical Overview

Below is a short summary of the technical solution as described in the following sections:

- Define clusters of BSW modules that contain preferably all three layers of a stack, or, if needed, a subset of modules of a stack (e.g. communication, memory, I/O stack).

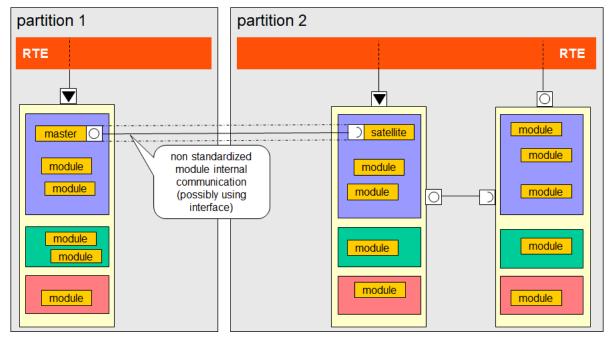

- Module entities can be split into a master and satellites, which are assigned to different BSW partitions. Masters and satellites can use non-standardized AU-TOSAR interfaces, for internal cross partition communication. The master/satellite approach is mainly used by distributed system service modules and for communication between BSW clusters of the same type.

The proposed solution meets the demands on performance and safety while minimizing the impact on already standardized BSW module interfaces ([RS\_BRF\_00206],

[RS\_BRF\_01160]). Most changes are hidden within modules (e.g. by providing master/satellite implementations) without affecting other modules. Interfaces between different modules do not change.

#### 2.1.3.1 BSW Functional Clusters

BSW functional clusters are groups of functionally coherent BSW modules. Each functional cluster includes a set of BSW modules. It is possible to have several BSW functional clusters of the same type (e.g. several I/O clusters in different BSW partitions), each using a different set of modules (e.g. IOHWA + ADC in one partition and IOHWA + ADC + DIO in the second partition).

The following types of clusters might be standardized in a later release:

- Communication cluster

- Memory cluster

- I/O cluster

- Watchdog cluster

The allocation of BSW functional clusters to BSW partitions is determined by the usage of BSW modules by the application software. Functional clusters can be allocated to different BSW partitions, and functional clusters of the same type can be available in several BSW partitions. Different functional clusters can be allocated to the same or to different BSW partitions.

The same functional cluster can only exist at most once per BSW partition.

BSW functional clusters are used by applications or other BSW modules to access buses, memory, I/O channels and watchdogs, and they are usually required in one or few BSW partitions only.

The introduction of BSW functional clusters does not change the existing AUTOSAR interfaces between the BSW and the RTE, which are mainly used to implement AUTOSAR services, i.e. to communicate with the application layer. It may however change the availability of standardized AUTOSAR interfaces on different partitions.

The internal structure of a BSW functional cluster, including its internal communication between BSW modules, and the communication with system services that the BSW functional cluster uses is not necessarily affected by the parallelization of the BSW, and it does not need to change. It may however be adapted, for example in order to fulfill special demands on concurrency like the support of different entities of the same module running in different partitions.

The communication and synchronization between modules in BSW functional clusters of the same type (e.g. in two communication clusters to support a gateway functionality) is not standardized. It will be implemented by communication between entities (e.g. by

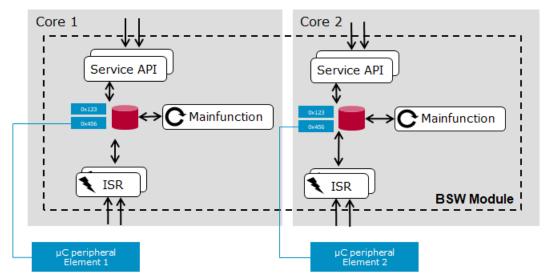

a master and satellites) of specific modules, which can use non-standardized interfaces for communication across BSW partition boundaries, see Figure 2.1.

Figure 2.1: Functional clusters of the same type

Modules that do not belong to BSW functional clusters (e.g. system services) will always be accessed within the same BSW partition where the BSW functional cluster is located. As the interfaces do not change, these modules must be locally available in each BSW partition, if needed.

#### 2.1.3.2 Inter-BSW-partition communication

Function calls to tasks that are supposed to be executed in a different BSW partition/ on a different core cannot be implemented as simple C calls to this function, because these calls would be handled on the local BSW partition.

The BSW Scheduler (SchM) therefore provides functions to invoke masters or satellites of the same module on different BSW partitions using either client-server or sender-receiver communication. Details on this API of the SchM are explained in subsection 2.2.3.

# 2.1.3.3 Determining the Partition for Service Execution

The actual BSW partition for the handling of an RTE event is determined by its task mapping. Basically, if an event is mapped to a task, it is executed within the partition assigned to this task. If an event is not mapped to a task, it is executed within the same

partition as the task that caused the event. Details on the task mapping are described in subsection 2.4.1 of this document.

Calls from BSW entities to other BSW entities are not mapped to a partition. They are executed wherever they are called. Therefore, several calls to a BSW function may be processed in parallel on different partitions and cores. Consequently such functions must be designed and implemented carefully w.r.t. parallel execution in different partitions; if necessary, they shall be reentrant or concurrency safe.

# 2.1.3.4 BSW partitions

Only partitions that have the configuration parameter <code>EcucPartitionBswModule-Execution</code> set to true can execute BSW modules. Such partitions are called BSW partitions. BSW partitions may additionally contain application software components above the RTE.

# 2.2 Parallel Execution of BSW modules

This is the chapter for developers of BSW modules.

#### 2.2.1 Core-Dependent Branching

Because entities of the same module share the same implementation, even if they are running on different cores, different behavior cannot be realized by different code. Instead, the specific behavior shall be determined by runtime information. It is possible for example to use the core id for this, i.e. branch the control flow depending on the return value of the OS APIs GetCoreID, or also GetApplicationID.

Another variant of implementing modules operating sharing the same implementation but running on different cores can be realized basing on a different core individual configuration. This requires to call the initialization routine Init per core passing a pointer to the according configuration. This design pattern is considered as ideal to implement a core-dependent branching for the MCAL.

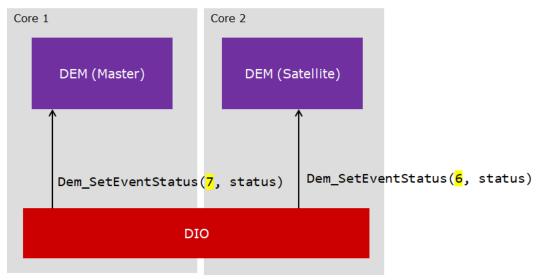

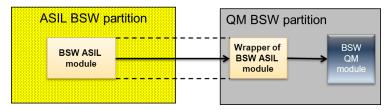

# 2.2.2 Master/Satellite-approach

Modules that need to be accessed in different BSW partitions can be implemented using the master/satellite pattern.

The distribution of work between master and satellite is implementation specific. One extreme is that the satellite only provides the interfaces to the other modules in the same BSW partition, and that it routes all requests to the master and answers back to the other modules. At the other extreme, the satellite can provide the full functionality

locally (e.g. local mode management for a complete application which runs in the same BSW partition) and only synchronizes its internal states with the master, if necessary. There might even be several masters for different functionality, e.g. two PduR masters for a distributed PduR gateway.

The master coordinates requests from the satellites and can filter or monitor incoming satellite requests. The master and one or several satellites are treated like being one module entity in some respect:

- Master and satellites are always vendor specific solutions, coming from the same vendor.

- The interfaces of master and satellite to other module entities in general are the same as specified in AUTOSAR for traditional modules. Master and satellite should provide the same APIs. This means that when migrating to partitioned systems, existing module entities can be replaced by a master and one or several satellites, in most cases without changing other modules. Exceptions might be module internal adaptations to additional delays which are caused by interpartition communication.

- Master and satellites have the same entry points in each BSW partition (i.e. they start executing the same functions from shared memory) and internally branch (e.g. by using the GetApplicationID API) to master or satellite specific code according to the OS-Application (partition) they run in. Depending on the build strategy, other implementations might be possible in multi-Core systems if each core can execute its own code. Also, satellites might share the same code without further branching.

- As an alternate realization the master- satellite approach could be implemented in a way that the master is realized as a satellite too, while the real master implementation consists of the BSW module kernel only so that all requests can be exchanged with this kernel. This approach is considered as ideal for MCAL implementations.

- The communication between master and satellites is not standardized. It is considered to be module-internal and is not visible to other modules.

- The communication between master and satellite can be initiated in either direction (i.e. by both the master and the satellites), as well as from one satellite to another one.

- All interfaces between masters and satellites are only allowed to be connected within the same distributed module.

- The communication between master and satellites can be implemented within one BswModuleEntity, or between different BswModuleEntitys that belong to the same BSW module.

- Depending on the application, usage of master/satellite may be appropriate or not. For example, it may be more efficient to use separate, partition specific

watchdog clusters, which work independently from each other, rather than using the Watchdog Manager in a master/satellite approach.

The master is the part of a distributed BSW module that coordinates requests by satellites and can filter or monitor incoming satellite requests. This may result in additional fault detection or fault mitigation mechanisms. Generally, all errors caused by distributed execution of a module should be handled module internally.

The master/satellite implementation is the standard solution for system services in partitioned systems.

Specific drivers also might have to provide local satellites, if the hardware can only be accessed from a different core. The standard solution, if possible, is to execute the same multi-core reentrant function in each partition and to separate the data to work on into disjoint sets, one for each partition. For example, the COM module may work on all IPDUs assigned to the bus that the BSW functional cluster of this module belongs to. Concurrent access to the same hardware or shared data needs to be protected, e.g. by ExclusiveAreas in this case.

In specific cases, modules within BSW functional clusters also need to be implemented as master/satellite, if the BSW functional clusters are duplicated and the entities in different BSW partitions need to be synchronized or need to exchange data. This might apply to the Watchdog Manager, the NVRAM manager, and to network and state managers in duplicated communication clusters. COM modules also might need to have a master and a satellite to implement cross partition gateway functionality.

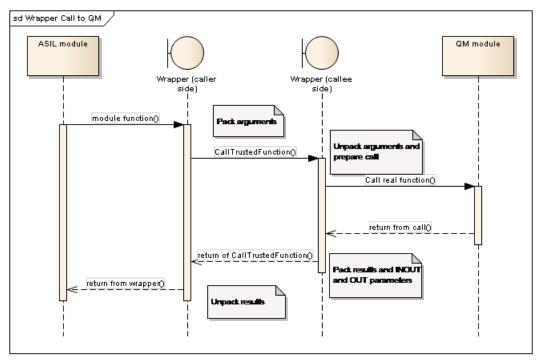

#### 2.2.3 Using the BSW Scheduler for Inter-Partition-Communication

The BSW Scheduler (SchM) provides a number of functions to support communication between BSW module entities that are executed in parallel. More precisely, it provides the following methods to handle synchronous and asynchronous calls (including callbacks) as well as sender-receiver communication.

The functionality is generally similar to that of function calls between SWCs and the BSW. However, because the RTE may not be available at certain points of time (especially during startup of an ECU), this functionality must be available within the BSW itself.

```

• Std_ReturnType SchM_Call_<bsnp>[_<vi>_<ai>]_<name>(

[OUT <typeOfReturnValue> returnValue]

[IN|IN/OUT\|OUT]<data_1> ... [IN|IN/OUT|OUT] <data_n>)

Or

Std_ReturnType SchM_Call_<bsnp>[_<vi>_<ai>]_<name>(

[IN|IN/OUT\|OUT]<data_1> ... [IN|IN/OUT|OUT] <data_n>)

```

Invoke a client-server-operation, possibly crossing partition boundaries. The actual parameters  $data_1 \dots data_n$  are information that is passed [IN] and/or re-passed [IN/OUT | OUT] to/from the called service.

The presence of the parameter returnValue and its type <typeOfReturnValue> depend on the called service. For synchronous calls, the parameter is present and <typeOfReturnValue> is the type returned by the called service. For asynchronous client-server-operations and operations with return type void, the parameter is omitted.

Callback from an asynchronous client-server-operation, possibly crossing partition boundaries.

The receiver of a callback is determined by the AsynchronousServerCallResult Point of this callback. The AsynchronousServerCallResultPoint refers to the originating AsynchronousServerCallPoint, which in turn "knows" the calling module entity.

```

Std_ReturnType SchM_Send_<bsnp>[_<vi>_<ai>]_<name>(IN <data>)

Write data to a sender-receiver link between BSW modules, possibly crossing partition boundaries.

```

• Std\_ReturnType SchM\_Receive\_<bsnp>[\_<vi>\_<ai>]\_<name>(OUT <data>)

Read data from a sender-receiver link between BSW modules, possibly crossing partition boundaries.

#### 2.2.4 Using Shared Buffers (in systems without memory protection)

In systems without memory protection between the BSW partitions, system services and all BswCalledEntities can be called directly in every partition, including the complete call tree. This requires a reentrant, concurrency safe implementation.

The services and other called entities might work on module internal data, which is shared between different entities of the same module. All access to such data must be protected by ExclusiveAreas. Appropriateness of concrete protection mechanisms depends on the possible kinds of access. For example, concurrent writing generally needs to be prohibited, whereas concurrent reading may be acceptable, as long as only one partition writes at the same time.

BswSchedulableEntities are located on one core only and process the data periodically or event driven.

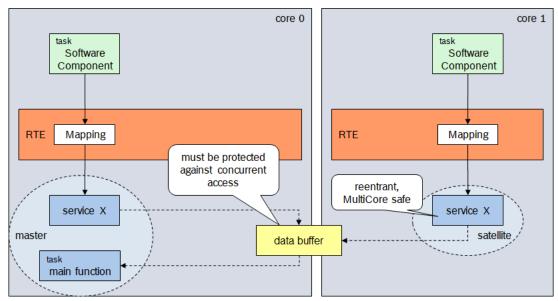

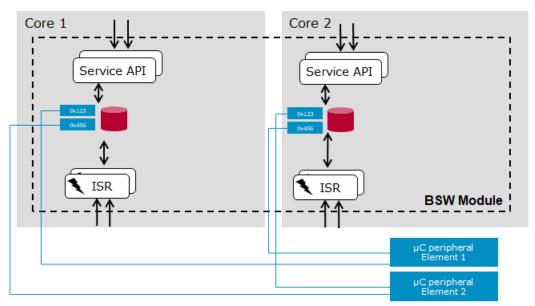

Figure 2.2: Invocation of same service on different cores

Figure 2.2 shows the example of a service "X", where the same API and the same code is called directly by the RTE on different cores. This is the default, if the services (respectively the OperationInvokedEvents) are not mapped to a task.

The code must be reentrant and concurrency safe, which means that all access to data must be protected against concurrent access by the same or by a different entity of the same module.

In this example, the same service "X" (BswCalledEntity) writes into a module internal data buffer accessible from core 0 and from core 1. A "main function" (BswSchedu-lableEntity), which is mapped to a task, reads the data from the buffer for further processing. In order to prevent read/write-conflicts, this "main function" must be protected from reading the buffer while it is written.

This can be considered a special case of the generic master/satellite approach for systems without memory protection between the BSW partitions.

The advantage of this approach is that the original, unchanged modules can be used, as long as they are implemented concurrency safe, which is usually the case for single core already, if different entities of the same module work on the same data, as shown in the example for core 0. Compared to the AUTOSAR R4.0 solution, where all service calls have to be routed to the master core, the performance can be improved considerably without much effort (assuming there is no need to do cross-core communication later).

The following must be considered for a concurrency safe, reentrant implementation:

- Access to all shared resources, e.g. buffers, is protected by ExclusiveAreas.

- Call trees can be made multi-core safe, if either called entities are safe, or calls are protected by ExclusiveAreas (if lock times stay within a specified limit).

BswCalledEntities that are available to CDDs can also be called directly by the CDD. The same rules apply as in R4.0.

The SchM must support cross core ExclusiveAreas, implemented by protected Spinlocks. A protected spinlock is an exclusive area that has "OS\_SPINLOCK" as its value of RteExclusiveAreaImplMechanism. This kind of exclusive areas is available for controlled access by BSW modules only. Protected spinlocks are handled by the Basic Software Scheduler.

# 2.2.5 Accessing Hardware/Drivers

BswModuleEntitys of the MCAL (drivers) shall be accessed in the following way:

- Access by the BSW functional cluster within the BSW partition where the caller is located. So for example the FLS driver belongs to the BSW functional cluster "Memory". In case of NVM access, the NVM module might be provided on all cores as a master/satellite implementation. The master uses the FLS driver on a single core only. So the FLS driver is available on exactly that core.

- Any BSW required by the application shall be accessed in the BSW partition where the caller is located. For example I/O drivers such as DIO, ADC and PWM can be used by any core / partition. These are either realized as master/satellite implementation or as a redundant implementation per core basing on atomic access to the hardware.

The detailed realization of the MCAL multi-core approach is described in section 2.5 "MCAL Distribution".

#### 2.2.6 Concurrency safe implementation of modules

Concurrency safety of BSW modules respectively the functions implemented by these modules may be achieved by different mechanisms.

Generally, the following levels of reentrancy can be distinguished according to [TPS\_BSWMDT\_04103]. The concrete level of a BswModuleEntity is defined in the optional attribute "reentrancyLevel".

- Multi-core reentrant: Unlimited concurrent execution of an interface is possible, including preemption and parallel execution on multi-core systems. This level can be either achieved by mutual exclusion when entering critical regions, or by the absence of such regions, for example if there are no shared resources (including hardware and memory).

- Single-core reentrant: Pseudo-concurrent execution (i.e. preemption) of an interface is possible on single core systems. This is the highest level of reentrancy defined by AUTOSAR 4.0.3. Because it does not explicitly cover multi-core systems, "concurrency safe" has been introduced additionally. This level can gener-

ally be ensured by the same mechanisms as "concurrency safe", but they must be ensured to work across core boundaries.

• **Non-reentrant:** Concurrent execution of this interface is not possible.

If a module that is not concurrency safe is invoked in different partitions, there is no warranty that the module will uphold its desired behavior. In this case, correct behavior shall be ensured by the usage of the module, for example if the caller(s) prevent parallel execution by using exclusive areas.

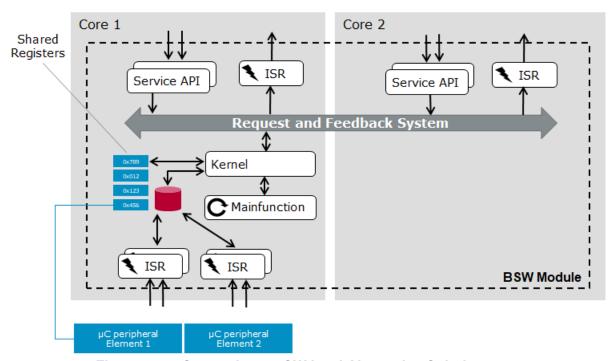

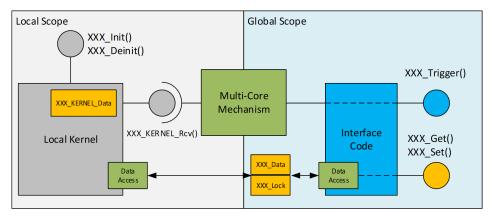

#### 2.2.7 Kernel based Master-Satellite Realization

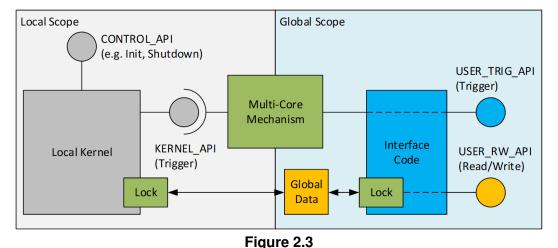

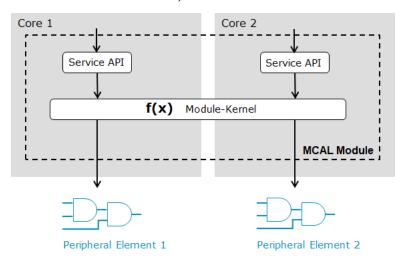

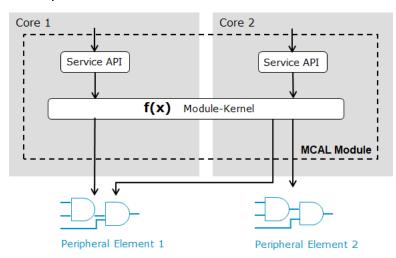

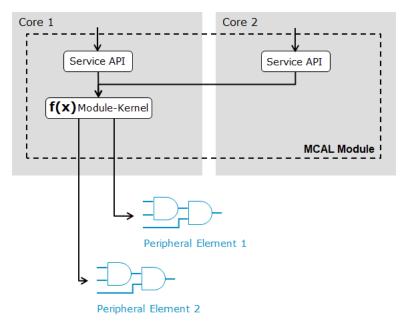

One way of realizing the master-satellite concept is the implementation of a module split into kernel and according interfaces, which are provided for all partitions the module shall be used from. The focus of the chapter is to describe the idea of the distribution of the according BSW module as a guidance for similar cases.

In a first step the service API's are categorized, e.g. according to MCAL distribution concept:

- Service API required by multiple cores / partitions for triggering and reading / writing of data

- Service API which are required by one partition only (e.g. initialization, shutdown)

This will lead to the following BSW module architecture:

In the second step the SW designer needs to select an according BSW distribution pattern for each service API following the below listed categories:

- Trigger a control flow from service API to kernel API (if required including data)

- Read of a symbol from a global buffer

- Write a symbol to a global buffer, which is later-on polled by the kernel

For reading and writing data, one will typically implement according get and set operations into the interface part of the BSW module, adding an according data protection mean (e.g. spinlock) if necessary.

For transferring control flow, one will implement on the one hand side the user API operation and on the other hand the same operation inside the kernel API. The relation can be 1:1 (one user API matches one kernel API) or n:1 (several user API match one kernel API).

All local API have to be allocated with local core scope and all global API with global core scope applying the memory allocation specification (AUTOSAR\_SWS\_Memory Mapping, see [2]).

Applying this idea to the PWM driver, one would get the following API distribution:

# Control API with local scope:

| CONTROL API                     | Core Scope                       |  |

|---------------------------------|----------------------------------|--|

| Pwm_Init                        | local (same partition as kernel) |  |

| Pwm_DeInit                      | local (same partition as kernel) |  |

| Pwm_Main_PowerTransitionManager | local (same partition as kernel) |  |

Note that these API's are restricted to the local kernel partition. The task calling the transition manager needs to be scheduled within the same partition / on the same core.

# User read/write API with global scope:

| USER_RW API              | Access / Core Scope                |

|--------------------------|------------------------------------|

| Pwm_GetOutputState       | read global data                   |

| Pwm_GetCurrentPowerState | read global data                   |

| Pwm_GetTargetPowerState  | read global data                   |

| Pwm_GetVersionInfo       | read static information            |

| Pwm_DisableNotification  | write to global data (atomic flag) |

| Pwm_EnableNotification   | write to global data (atomic flag) |

Note that these API's are available to any partition, so these are also used if the call is done from the same partition where the kernel resides.

User trigger API with global scope and related kernel API with local scope:

| USER_TRIG_API / Global Scope | KERNEL_API / Local Scope     |

|------------------------------|------------------------------|

| Pwm_SetDutyCycle             | Pwm_Kernel_SetValues         |

| Pwm_SetPeriodAndDuty         |                              |

| Pwm_SetOutputToIdle          | Pwm_Kernel_SetOutputToIdle   |

| Pwm_SetPowerState            | Pwm_Kernel_PowerStateManager |

| Pwm_PreparePowerState        |                              |

Note that the USER\_TRIG\_API is available to any partition, so these are also used if the call is done from the same partition where the kernel resides. The KERNEL

API however is not accessible to the user. It is internal only. The calls from the local partition are passed through the USER TRIG API.

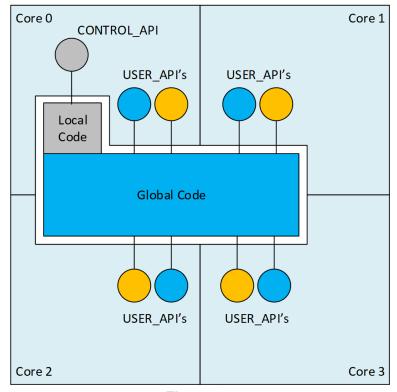

Finally, the picture below shall summarize the interface availability along the cores / partitions for the given example, while the kernel API is hidden inside the BSW module not visible to the outside.

Figure 2.4

The following points shall be noted in addition:

- All user callbacks shall be called in the local partition. The user needs then to

provide similarly a service API with global scope, which can be called. This is

useful as the implementer of each BSW module or CDD knows ideally how its

module is designed. Doing the other way around could waste CPU resources

instead as caller and called module might implement the partition transfer twice.

- It is strongly not recommended to apply this or other master-satellite concepts for crossing partitions on the same core, e.g. motivated by safety, as this will also waste CPU resources.

When choosing the according protection and multi-core means one shall always try to achieve a blockade free implementation to allow parallel operation along multiple cores.

# 2.2.8 Atomic Operations Library

Introducing the BMC Libray, AUTOSAR now provides a multi-core atomic library. The interfaces of this library cover similar use cases / interfaces as the C11 standard atomic library (http://en.cppreference.com/w/c/atomic).

The library shall support developers implementing efficient lock-free implementations and so ease the implementation of distributed BSW (Master/Satellite) without the use of a heavy weight mutex.

Atomic operations typically perform a read-modify-write sequence on a memory address. For example, an atomic increment loads a value, increments it, and stores the result in such a way that no other thread can modify the value in the middle. So, a cross-core set request can be realized with atomic operations in an efficient way.

#### 2.3 SchM Interfaces for Parallel BSW execution

This chapter describes the extensions to the SchM required by the concept "Enhanced BSW allocation".

The Basic Software Scheduler (SchM) is responsible for handling the inter-partition communication between BSW modules. This is conceptually similar to the handling of inter-partition communication between SW-Cs by the RTE. Because the BSW modules are arranged below the RTE in the AUTOSAR architecture however, the communication must be available before the RTE is available. Therefore and for reasons of performance, BSW modules use the SchM for communication.

For the distribution of BSW modules across several partitions, the SchM shall implement the methods <code>SchM\_Call</code>, <code>SchM\_Result</code>, <code>SchM\_Send</code> and <code>SchM\_Receive</code>, which are used to handle service calls and callbacks as well as writing data to and reading data from a sender-receiver connection. For details on the signatures of these functions, please refer to subsection 2.2.3, which describes the SchM extensions from a BSW developer's point of view.

The SchM can use IocSend (a direct call to the OS) to send data in inter-partition communication. Other RTE internal mechanism might not be available during startup.

The Inter-OS-Application Communicator (IOC) shall be configured to provide <code>Ioc-Send\_<Id>functions</code> with a uniquely determined <code><Id>for</code> all client-server and sender-receiver connections that cross partition boundaries.

Analogously, the SchM shall use <code>IocReceive</code> to receive data from inter-partition communication, and the IOC shall provide the corresponding <code>IocReceive\_<Id> functions</code>.

The following frame contains some pseudo code snippets that show how to use the IOC for inter-partition communication.

```

void some_BSW_function() {

```

```

char *str = "some text";

SchM_Send_Data_Src_DstN(str);

4 }

6 Std_ReturnType SchM_Send_Data_Src_DstN(char *str) {

IocSend_1(str, 5);

ActivateTask(TASK1);

8

10

11 Std_ReturnType SchM_Receive_Data_Src_DstN(char *str) {

13 }

14

15 TASK (TASK1) {

char data[20];

SchM_Receive_Data_Master_Sat1(data);

/* do something with data */

20 }

```

# 2.4 Configuration of Basic Software in Partitioned Systems

This is the chapter for integrators.

# 2.4.1 Task Mapping

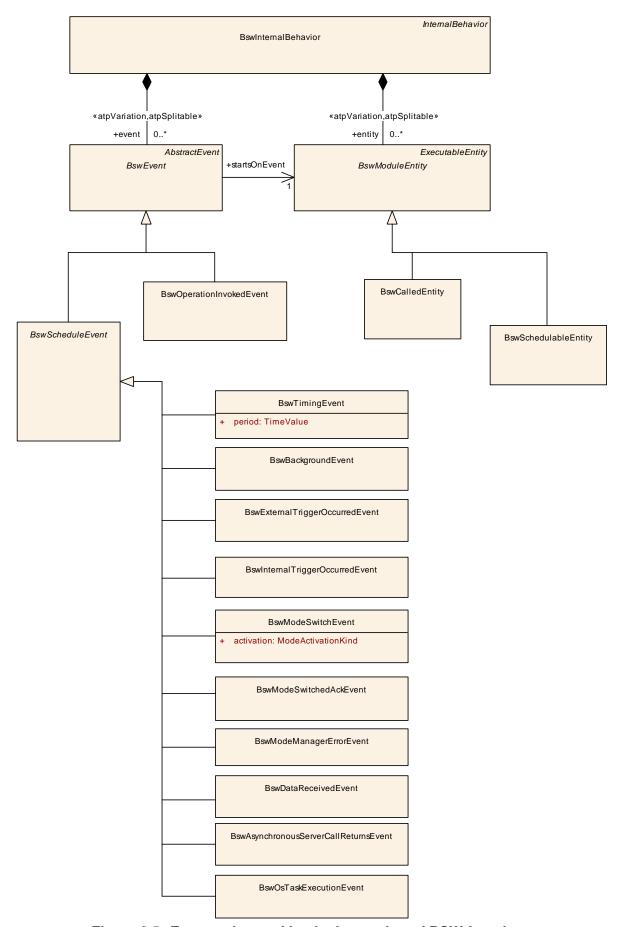

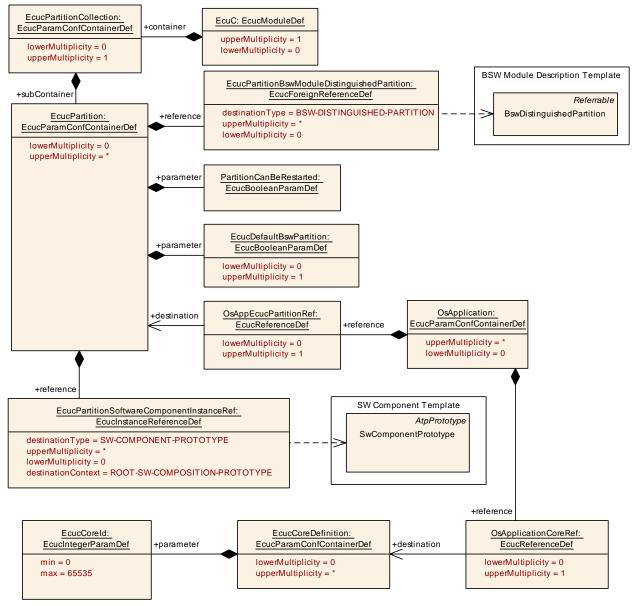

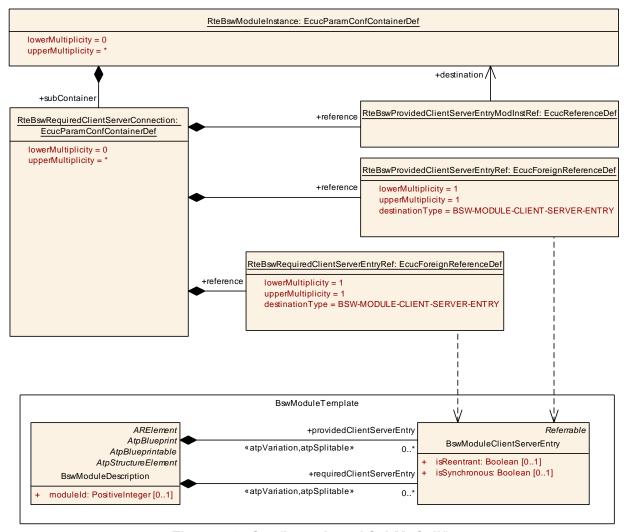

The parallelization of BSW modules introduces several new subclasses of BswEvent to the AUTOSAR metamodel. These classes are shown in Figure 2.5. Each BswEvent (including instances of subclasses of BswEvent) is assigned to a BswSchedula-bleEntity, which is started upon occurrence of the event.

Figure 2.5: Events triggered by the invocation of BSW functions

Document ID 631: AUTOSAR\_EXP\_BSWDistributionGuide

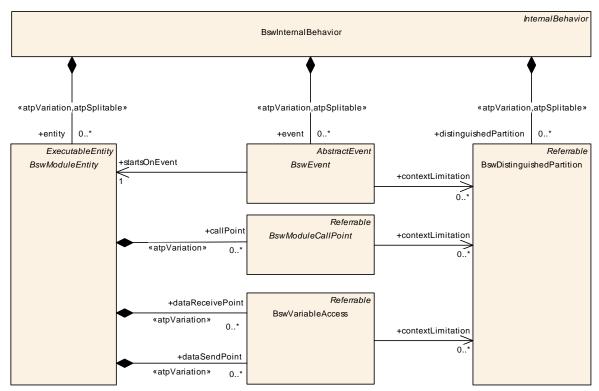

A more fine grained description of the partition specific behavior of an entity can be described by the use of <code>BswDistinguishedPartitions</code>, as shown in Figure 2.6. A <code>BswDistinguishedPartition</code> is the abstract representation of a partition, which allows to the mapping of a specific <code>BswEvent</code>, <code>BswModuleCallPoint</code> or <code>BswVari-ableAccess</code> to a set of abstract partitions. The representation of a partition at this point is an abstract one in the sense that it is part of the BSW module description (according to the module description template), whereas a concrete partition is determined at ECU configuration time.

For example, if a module entity running in partition 1 provides data via a VariableData Prototype to the same entity running in partitions 2 and 3, the BswModuleEntity aggregates a dataSendPoint with a contextLimitiation to partition 1 and a dataSend Point with a contextLimitation to partitions 2 and 3.

Figure 2.6: Modeling partition specific properties of entities using BswDistinguished-PartitionS

The actual partition for the handling of an event is determined by its task mapping.

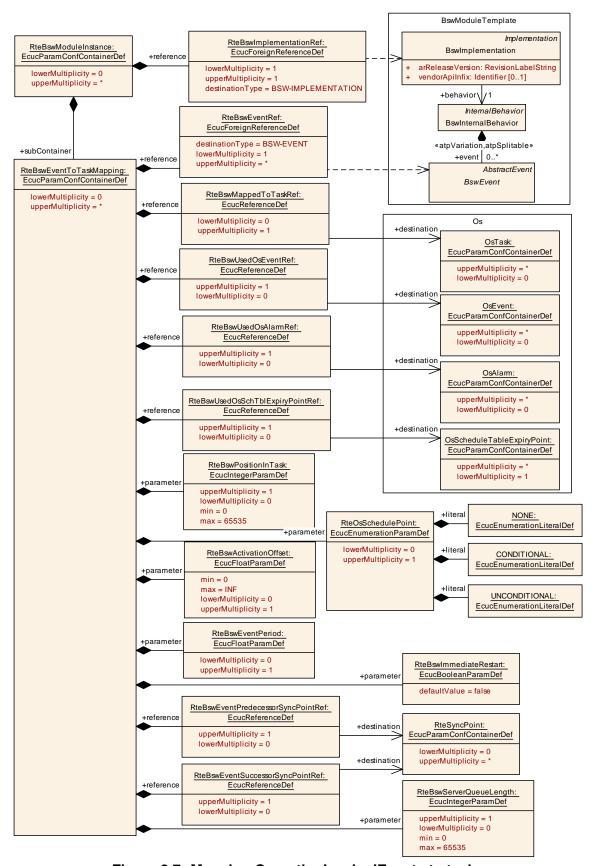

Figure 2.7: Mapping OperationInvokedEvents to tasks

# Figure 2.7 shows the corresponding excerpt from the AUTOSAR metamodel.

An RteBswEventToTaskMapping refers to a BswEvent (indirectly via its RteBsw-EventRef) and to an OsTask (also indirectly via its RteBswMappedToTaskRef). The task is in turn mapped to a partition, and the partition is mapped to a  $\mu$ C core, which is the core responsible for the processing of the event. Mapping an event to a task is optional; if an event is not mapped to a task, it is handled in its originating partition. If no special mechanisms apply that prevent concurrent execution, a prerequisite for a non-mandatory mapping of an event to a task is:

- if the BSW entity is shared between multiple BSW partitions the entity needs to be *concurrency safe*

- in case it is exclusively available only on one BSW partition it needs to be at least reentrant.

Please note that it is currently not allowed to map RunnableEntities of a SW component to multiple partitions [SWS\_Rte\_07347]. For BSW it is possible to map the same module entities to different tasks and partitions by using different BswEvents referring to the same entity

# 2.4.2 General Configuration of Master and Satellites

Modules that shall be available in multiple partitions can be implemented as masters and satellites. In this case, the master and all satellites of the same module share the same code (which may implement core-dependent behavior however) and the same configuration. Hence, a master and its satellites are treated as one module entity w.r.t. their configuration.

The communication between master and satellites is not to be standardized. It is considered to be module-internal and it is not visible to other modules. However, since it is recommended to use SchM mechanisms for internal communication, the non-standardized client-server entries and data accesses in the BSWMD to connect master and satellite need to be configured.

# 2.4.3 Configuring the BswM (per Partition)

On systems with distributed BSW there is one BSW Mode Manager (BswM) per partition (but one OS and EcuM per core, which is the same as long as we have one BSW partition per core). Each of these BswMs can be configured independently. A BswM mainly interacts with the state managers (ECU state manager and bus state managers, for instance) on the same partition.

The BswM is also responsible for the initialization and shutdown of BSW modules running in the same partition. Therefore, its configuration depends on the mapping of BSW modules to partitions.

The configuration of the BswMs is split across the container <code>BswMGeneral</code>, which contains shared configuration parameters of all BswM entities and <code>BswMConfig</code> containers, where one <code>BswMConfig</code> is defined for each BswM entity. Consequenty, the mapping of a BswM to its partition is defined in the corresponding <code>BswMConfig</code> container, which has a <code>BswMPartitionRef</code> pointing to the respective partition. This mapping of BswM configurations to partitions ensures that for every partition the correct configuration of the BswM can be determined.

Additional extensions to the BswM configurations for the allocation of BSW modules to multiple partitions are

- A reference BswMRequestRemoteMode in the container BswMAvailableActions. This action indicates a call to a BswM in a different partition, which is used to propagate mode requests.

- References BswMBswMModeRequest and BswMBswMModeSwitchNotification in the container BswMModeRequestSource. The BswMBswMModeRequest indicates that the source of a mode request is a BswM running in a different partition ([ECUC\_BswM\_00980], cf. [3]). BswMBswMModeSwitchNotification indicates that another BswM has switched a mode.

- All functions listed in an action list that is processed by a BswM entity must be available in the partition this BswM is running in.

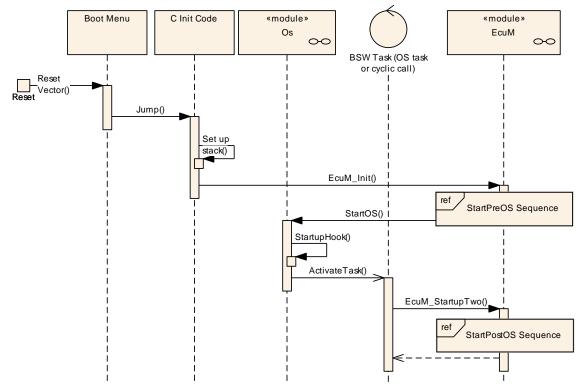

#### 2.4.4 Configuring the EcuM (per Core)

On systems with distributed BSW there is one EcuM per core (even if there are multiple BSW partitions on that core). In other words, on every core there shall be one and only one partition that runs the EcuM. The partition running the EcuM is determined by the EcuMFlexEcucPartitionRef, which is specified in the container EcuMFlexUser-Config of the EcuM configuration.

On architectures with a sequential start of cores, there is one designated master core in which the boot loader starts the master EcuM via <code>EcuM\_init</code>. The EcuM in the master core starts some drivers, determines the Post Build configuration and starts all remaining cores with all their satellite EcuMs.

On architectures where all cores are started at the same time, core dependent branching within the <code>EcuM\_init</code> function can be used to achieve core-specific behavior. This can in turn be used to identify the EcuM master (running on the master core), which is responsible for the EcuM initialization on the slaves.

#### 2.5 MCAL Distribution

#### 2.5.1 Introduction

Because it is required to provide access to hardware features from several cores and partitions the MCAL functionality needs to be provided to exactly that core it is required and where it is useful to provide the functionality. So consequently the distribution of MCAL modules is not identically done for all MCAL modules but needs to follow the needs of the functional clusters described in the chapters before. The following chapters shall guide through the classification of the required multi-core capabilities, introduce an according multi-core type which is assigned to the individual modules. Furthermore some basic design patterns shall be shown to allow the implementation of the required functionality.

It shall be noted that the introduction of the multi-core MCAL requires the introduction of asynchronously behaving interfaces to enable non-blocking parallel execution on multiple cores. These are introduced to the individual SWS of the affected AUTOSAR modules and not mentioned furthermore in the chapter below.

# 2.5.2 Assumptions of Use

To apply the MCAL distribution several assumptions of use shall be given, to define the boundary conditions of the MCAL environment:

- 1. A multi-partition (multi-application) AUTOSAR operating system is required to support the use cases defined within this concept.

- 2. The hardware implementation shall allow a mapping of peripherals at least to cores. In future it is expected that hardware implementations allow a mapping to cores and partitions.

- 3. It shall be possible to route hardware and software interrupts to one partition or at least a dedicated core (for further routing by the OS).

- 4. Service modules which are required by the MCAL drivers shall support multi-core use-cases by being able to accept calls to their service API's on respectively by any core. The relevant services are:

- Det

- Dem

- EcuM

- Os

- SchM

- NvM

Furthermore it is assumed that a multi-core microcontroller is used however this is not mandatory as the concept provides an identical set of service API's regardless whether it is a single- or multi-core implementation. Additionally it is possible to realize mixed ASIL systems with segregation in space and time where the mappable MCAL elements are assigned to the different partitions respecting the safety integrity level of the resulting MCAL implementation.

An example is a system with two partitions on one core which both access the MCAL. Without this concept, the driver must belong exclusively to one of the partitions, making partition crossings execution time expensive. With the new concept, MCAL elements can be individually assigned to the two partitions and thus eliminating the need to cross partition boundaries.

#### 2.5.3 Constraints

To realize the concept further constraints are defined to prevent inefficient and multicore blocking implementations. In this sense it is especially important to consider that it is not sufficient anymore to implement exclusive areas on a single core but to additionally ensure an access serialization in case resources need to be shared across several partitions distributed to several cores.

- Access Serialization on a single core: For single-core systems concurrency problems are well understood and mitigated by exclusive areas, which limit concurrent access to one process at a time. This is typically done by locking interrupts, employing OS resources or creating a non-pre-emptive scheduling. This effectively means access-serialization of the different processes.

- Access Serialization across cores: Since exclusive areas only have a core-wide scope, they are not sufficient to prevent concurrent access in multi-core environments. But as soon as it is required to access the same resource (e.g. by access to the service API's, processing of the ISRs and main-functions) it is required to introduce cross-core means. Besides the usage of atomic resources, the worst because blocking one would be the introduction of a cross-core exclusive area by using a semaphore (spin lock) which would block several cores. Instead a better option would be a classical master-satellite implementation basing on a proprietary lean IOC.

As a summary, exclusive areas could technically be extended for multi-core scope however these would be implemented, but these would cause a significant performance drawback as two or even multiple cores would be blocked. So the concept will describe according design patterns showing the optimal protection means aligned to the defined multi-core types within this chapter.

#### 2.5.4 Definition of MCAL Users

There are the following different MCAL users to be considered:

- Application SWC (above the RTE) via IoHwAbstr

- CDD or BSW Module (below the RTE)

So the MCAL multi-core support needs to be provided independently of the RTE to cover both the use-cases.

# 2.5.5 Multiple Partitions versus Multi-Core MCAL

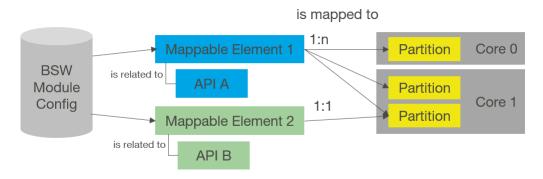

### 2.5.5.1 Considering Multiple Partitions

As the AUTOSAR standard allows the definition of multiple partitions per core, the MCAL distribution concept needs to respect this idea for the purpose of later extensions motivated for example by safety distribution. So, this concept implements the following idea:

- Mappable elements are not simply mapped to cores, but instead to partitions.

This is to allow, that one is able to implement further isolation features to the MCAL at a later point in time to ensure for example freedom from interference in between ADC channels.

- 2. MCAL interfaces instead are not mapped to partitions, but it is assumed that these are available on the cores where the user partitions reside. This results in the correct definition of the core scope, which is either GLOBAL or LOCAL. Simply spoken this means that interfaces required by partitions on a single core only, might be allocated with LOCAL scope. Instead interfaces required by different partitions on multiple cores shall be allocated with GLOBAL scope.

**Conclusion:** APIs are not mapped to partitions (just related to partitions). Mappable elements are mapped to partitions for further distribution needs.

# 2.5.5.2 Impact on MCAL Symbol Allocation

Respecting the idea of multi-core on the one and multiple partitions on the other hand will cause some influence on the mapping of MCAL driver internal data, constants as well as peripherals. Depending on the driver design as well as the hardware capabilities one can:

- 1. Map peripherals to cores or partitions, which might be protected by further hardware means, such as: privilege levels (hypervisor, supervisor, user, ...), safety partitions (by partition ID, task ID, ...) etc.

- 2. If required, allocate data in the individual partitions to ensure for example freedom from interference in between those. But allocate the data at least with the same core scope than the APIs using it. Map data and related operations to the same core.

Please note that allocating data to different partitions does not isolate those automatically. To achieve this an according memory protection is required in addition.

**Conclusion:** Symbols shall be allocated with the same core scope than the APIs (internal or public) using it.

### 2.5.6 Multi-Core Capabilities Classification Criteria

The following paragraphs are given to unify the understanding the required multi-core capabilities from different point of perspective.

# 2.5.6.1 Criteria 1 - APIs Availability

To classify the multi-core capability of a MCAL module it is first essential to understand the user expectation in the sense of "from what core the service API's shall be reachable". Out of this definition the following two cases can be derived:

- 1a: Local service API's (executable on one core only)

- 1b: Global (distributed /shared) service API's (executable on any core)

#### 2.5.6.2 Criteria 2 - MCAL Kernel Execution Context

Secondly one needs to understand where the MCAL module kernel shall ideally reside/located to limit the side effects of collisions on busses and bridges due to concurrent access to HW peripherals from several cores. Defining a local kernel does not exclude a multiplicity, to e.g. provide several kernels dealing with independent peripheral modules or core individual resources. The following cases are defined:

- 2a: One Local kernel (executable on one core only)

- 2b: Global (distributed /shared) kernel (executable on any core)

#### 2.5.6.3 Criteria 3 - HW Elements Mapping

As a third point one needs to consider the scope of mappable elements, refer to subsection 2.5.11, including its data to the according kernel instance. Taking this aspect into account, one extends the classification according to the hardware capabilities in terms of mapping of HW peripherals to cores. Here not only the pure hardware capability needs to be considered but also the performance impact of the according mapping. The following cases are defined:

• 3a: One HW element mappable to one core only

• 3b: One HW element mappable to several cores

# 2.5.6.4 Multi-Core Capabilities Classification Summary

The following table summarizes the scope of the required options for the shown criteria.

|                          | One Core Only | Several Cores |

|--------------------------|---------------|---------------|

| APIs                     | 1a            | 1b            |

| Kernel Execution Context | 2a            | 2b            |

| HW Elements              | 3a            | 3b            |

**Table 2.1: MC Capabilities Criteria**

# 2.5.7 Definition of MCAL Multi-Core Types

The following paragraphs introduce according multi-core types to be applied to MCAL modules classifying the according multi-core capabilities.

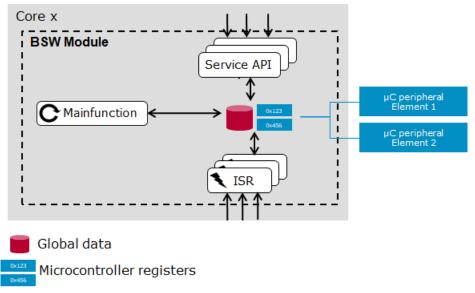

# 2.5.7.1 MCAL Multi-Core Module Type I

The MCAL modules are available on a single core only, the interfaces are not globally available.

The type is defined as a single-core module providing its service API's to one core only and implementing the kernel on exactly this core as the according HW elements shall be accessed by one core only.

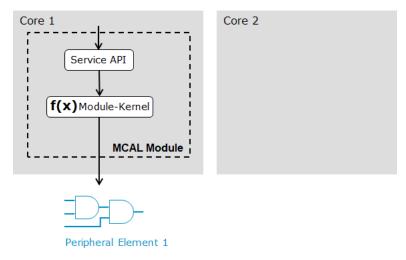

Figure 2.8: Type I

Examples of Type I are FLS, MEMIF and FEE. To limit the scope to this core, an according SwAddrMethod with local scope can be applied.

# 2.5.7.2 MCAL Multi-Core Module Type II

The MCAL modules provides a distributed kernel, executed per core, acting on individually mapped HW elements.

```

Type II = 1b + 2b + 3a

```

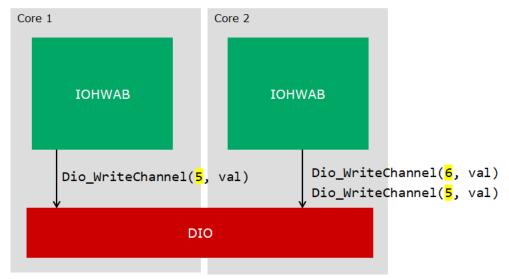

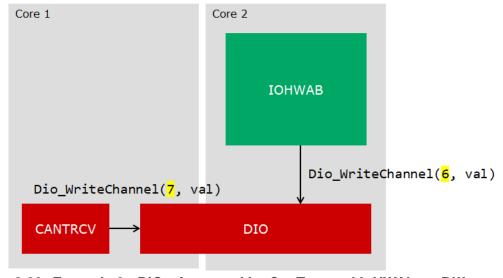

The type is defined as a special kind of a multi-core module providing its service API's as well as control API's (Init, DeInit etc.) on any core individual instance. So the action is performed on the core the action is triggered on. Each core instance operates on its own set of data. This especially makes sense for MCAL modules operating on HW elements which can be mapped to one dedicated core. A typical example for this type is, communication drivers such as CAN, ETH and FR.

Figure 2.9: Type II

#### 2.5.7.3 MCAL Multi-Core Module Type III

The MCAL modules provides a distributed kernel executed per core acting on globally available HW elements.

The type is defined as a special kind of a multi-core module providing its service API's on all cores but implementing the kernel in a global manner so that the action is performed on the core the action is triggered on directly accessing the globally available HW elements, mappable to any core including the related data. The according control

API's (Init, DeInit etc.) instead are available on one single core only. Especially in case the HW can be accessed atomically this module type is considered as useful. The most prominent example is the DIO driver.

Figure 2.10: Type III

# 2.5.7.4 MCAL Multi-Core Module Type IV

The MCAL module provides interfaces available on any core and one kernel on a single core accessing the mappable element by one core only

The type is defined as a special kind of multi-core module which provides its service API's across all cores but implements the kernel on one core only performing the access the mappable HW elements. The kernel could be allocated with the SwAddrMethod "local". This case requires proprietary multi-core means to perform synchronization (serialization) of requests towards the kernel. Such multi-core means could be a highly efficient message passing basing on polling or interrupts, a multi-buffering in combination with semaphores (for low recurrences). The according control API's (Init, DeInit etc.) of the type IV MCAL module are available on the core the kernel resides only with the according local scope. Examples for such a kind of BSW modules are ADC, PWM, ICU and OCU. This is a classical master-satellite implementation.

Figure 2.11: Type IV

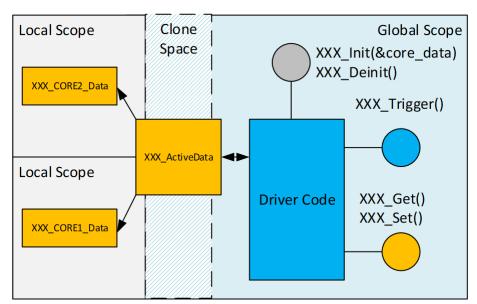

# 2.5.7.5 MCAL Multi-Core Module Type V

The MCAL module provides interfaces available on any core and multiple kernels on individual cores accessing the mappable element by the according core individually.

Type

$$V = 1b + 2a + 3b$$

This multi-core module is an extension of type IV which can be realized with HW implementations which allows a fully independent handling of peripheral modules or submodules. This is a rather academic constellation, no example picture is given.

# 2.5.7.6 MCAL Multi-Core Type Summary

The following table summarizes the scope of the defined MCAL multi-core module types:

|          | APIs             | APIs             |                  | Kernel Execution |                  | HW Elements      |  |

|----------|------------------|------------------|------------------|------------------|------------------|------------------|--|

|          | Only one<br>Core | Several<br>Cores | Only one<br>Core | Several<br>Cores | Only one<br>Core | Several<br>Cores |  |

|          | 1a               | 1b               | 2a               | 2b               | 3a               | 3b               |  |

| Type I   | Х                |                  | X                |                  | Х                |                  |  |

| Type II  |                  | Х                |                  | Х                | Х                |                  |  |

| Type III |                  | Х                |                  | X                |                  | Х                |  |

$\triangle$

| Type IV | X | Х | X |   |

|---------|---|---|---|---|

| Type V  | Х | Х |   | Х |

**Table 2.2: MC Capabilities Classification**

## 2.5.8 Mapping MCAL Modules to Multi-Core Types

The concept shall be generally applied to all MCAL drivers, which are listed in the following table:

| Module Abbreviation | MSN                           | SW Layer                      |  |

|---------------------|-------------------------------|-------------------------------|--|

| Adc                 | ADC Driver                    | I/O Drivers                   |  |

| Can                 | CAN Driver                    | Communication Drivers         |  |

| CanTrcv             | CAN Transceiver Driver        | Communication HW Abstraction  |  |

| CorTst              | Core test                     | Microcontroller Drivers       |  |

| Dio                 | DIO Driver                    | I/O Drivers                   |  |

| Eth                 | Ethernet Driver               | Communication Drivers         |  |

| EthSwt              | Ethernet Switch Driver        | Communication HW Abstraction  |  |

| EthTrcv             | Ethernet Transceiver Driver   | Communication HW Abstraction  |  |

| Fr                  | FlexRay Driver                | Communication Drivers         |  |

| FrTrcv              | FlexRay Transceiver Driver    | Communication HW Abstraction  |  |

| Gpt                 | GPT Driver                    | Microcontroller Drivers       |  |

| lcu                 | ICU Driver                    | I/O Drivers                   |  |

| Lin                 | LIN Driver                    | Communication Drivers         |  |

| LinTrcv             | LIN Transceiver Driver        | Communication HW Abstraction  |  |

| Mcu                 | MCU Driver                    | Microcontroller Drivers       |  |

| Mem                 | Memory Driver                 | Memory Drivers                |  |

| Ocu                 | OCU Driver                    | I/O Drivers                   |  |

| Port                | Port Driver                   | I/O Drivers                   |  |

| Pwm                 | PWM Driver                    | I/O Drivers                   |  |

| RamTst              | RAM Test                      | Memory Drivers                |  |

| Spi                 | SPI Handler Driver            | Communication Drivers         |  |

| Ttcan               | TTCAN Driver                  | Communication Drivers         |  |

| WEth                | Wireless Ethernet Driver      | Wireless Comm. Drivers        |  |

| WEthTrcv            | Wireless Ethernet Transceiver | Wireless Comm. HW Abstraction |  |

**Table 2.3: Relevant Modules**

To identify the multi-core type and mapping relation of the standardized MCAL modules one first needs to identify the HW "natural element" which shall be accessed by the module. Furthermore one need to identify the mappable element means the element which the user running on an individual core likes to access. Out of the definition one can then derive the relation of mappable elements to cores. Here the mappable element (ME) is shown in relation to the number of cores (Core) it can get mapped to. As a final conclusion the according multi-core type is shown required to derive a later design pattern recommendation for implementing the according AUTOSAR module.

| Driver   | HW "Natural"<br>Element                     | Mappable Element (ME) | Relation (ME : Core) | Multi-Core Type |

|----------|---------------------------------------------|-----------------------|----------------------|-----------------|

| Adc      | HW Units                                    | Channel group         | n:m                  | Type IV         |

| Can      | CAN Controller                              | Network               | n:1                  | Type II         |

| CanTrcv  | Transceiver ASIC                            | Network               | n:1                  | Type II         |

| CorTst   | Core                                        | Core                  | 1:1                  | Type II         |

| Crypto   | HW based: HSM                               | Job                   | n:1                  | Type II         |

|          | SW based: Job                               |                       |                      |                 |

| Dio      | Port / Channel (HW dependent)               | Port / Channel        | n:m                  | Type III        |

| Eth      | MAC                                         | Network               | n:1                  | Type II         |

| EthSwt   | Switch ASIC                                 | Network               | n:1                  | Type II         |

| EthTrcv  | Transceiver ASIC                            | Network               | n:1                  | Type II         |

| Eep      | EEPROM Driver                               | MCAL Module           | 1:1                  | Type I          |

| Fls      | Flash                                       | MCAL Module           | 1:1                  | Type I          |

| FlsTst   | Flash Test                                  | MCAL Module           | 1:1                  | Type I          |

| Fr       | Controller                                  | Network               | n:1                  | Type II         |

| FrTrcv   | Transceiver ASIC                            | Network               | n:1                  | Type II         |

| Gpt      | Timer Resource                              | Local Timer           | n:1                  | Type II         |

|          |                                             | Global Timer          | 1:m                  | Type III        |

| Icu      | Timer / Edge Detector                       | ICU Channel           | n:m                  | Type IV         |

| Lin      | Lin Channel                                 | Network               | n:1                  | Type II         |

| LinTrcv  | Transceiver ASIC                            | Network               | n:1                  | Type II         |

| Mcu      | Core                                        | Core, System          | 1:1                  | Type II         |

| Mem      | Memory, e.g. Flash                          | Memory Instance       | n:1                  | Type II         |

| Ocu      | Timer                                       | OCU Channel           | n:m                  | Type IV         |

| Port     | Port / Channel (HW dependent)               | Port / Channel        | n:m                  | Type III        |

| Pwm      | Timer                                       | PWM Channel           | n:m                  | Type IV         |

| RamTst   | Core                                        | Core, System          | n:1                  | Type II         |

| Spi      | Channel (for individual sequences) / Device | Spi Device            | n:m                  | Type IV         |

| Ttcan    | CAN Controller                              | Network               | n:1                  | Type II         |

| Wdg      | Watchdog Driver                             | Watchdog Resource     | n:1                  | Type II         |

| WEth     | MAC                                         | Network               | n:1                  | Type II         |

| WEthTrcv | Transceiver ASIC                            | Network               | n:1                  | Type II         |

**Table 2.4: Relevant Modules**

As a conclusion drivers belonging to type I which are consequently not impacted by this concept are listed below. For each driver, a rationale is given why it is deemed to be not relevant.

- Eep (EEPROM Driver): Memory services (NvM) are bound to one core. Hence there is no need for multi-core functionalities of the driver.

- Fls (Flash Driver): Memory services (NvM) are bound to one core. Hence there is no need for multi-core functionalities of the driver.

• FIsTst (Flash Test): Flash Test offers no potential for additional (application) use cases. Its purpose is to Check the functionality of the microcontrollers' flash memory as kind of a service. There are typically no SW functionalities realized with this module.

Note: As for future implementations of Wdg it is obvious to support multiple watchdogs on a multi-core system the multi-core type II is assigned even if it is today mostly a single-core implementation according to type I.

# 2.5.9 Seperation Stragies and Mapping of Elements

The challenge of the MCAL multi-core distribution is how to deal with global resources. These are:

- Global data

- Shared special function registers

- Peripheral registers

According to the given constraints in the chapters before it is obvious that two process contexts will access an identical global resource simultaneously. This can lead to:

- Corrupted data (Especially a problem with complex (non-atomic) data types.)

- Part of the data is written by the first process; another part is written by a second process.

- Only part of the data is written, and then the writing process is pre-empted, leaving a corrupt data-set.

- Races with read-modify-write data:

- Data written by a process (e.g. increment of a value) gets lost due to two interleaved read-modify-write operations.

In MCAL drivers, there are up to three elements which can have their own process contexts:

- Main function: Mapped- and executed in task context

- Service API: Called in the context of one or several tasks or ISR

- Interrupt Service Routine: Called in interrupt context

Especially service API's might be called in several process contexts. Depending on the architecture and functionality realized by the SW.

This chapter describes the multi-core capabilities according to the mappable element (which corresponds to the functional elements) which are mentioned earlier in this document and which shall be annotated to the MCAL driver. In addition the chapter defines basic separation strategies required to implement the mappable elements.

#### 2.5.10 Separation Strategies

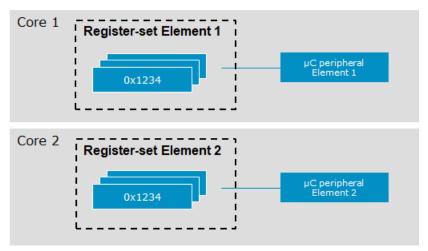

#### 2.5.10.1 Separation on HW Level

One of the ideal ways to be able to realize a multi-core implementation according to the defined multi-core-types is by distribution/separation on hardware level.

Ideal case is when the HW supports distribution/separation of physical peripherals, i.e. mapping peripheral modules to individual cores.

Note: This HW level separation requires independed register-sets of the individual peripheral which can be controlled from one core without impacting another one as shown in Figure 2.12.

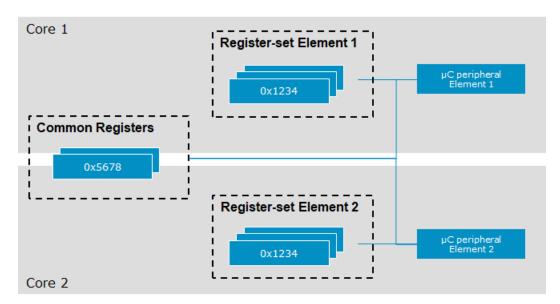

Figure 2.12: Independent Register-Set HW Level Separation

As shown in Figure 2.12, the register-sets behind the individual hardware/peripheral elements are independent of each other and so can be considered as mappable element. Mappable element means, one element can be mapped to a certain core exclusively. In case the register-set element allows an atomic access, mapping to multiple cores can be supported with this separation approach too.

#### 2.5.10.2 Separation on SW Level

Not all microcontrollers provide strictly separated register sets, respectively functionality of the hardware element (peripheral, core, memory). Typically those hardware elements require a common set of registers to control the functionality which cannot be atomically accessed .This is the case for several peripheral modules and peripheral features. Due to that a separation by software is required.

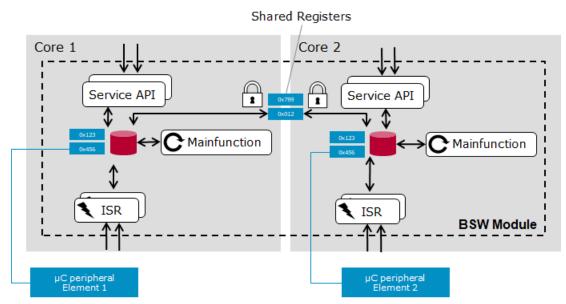

Figure 2.13: Shared Register-Set Separable on SW Level

For that purpose a software design pattern needs to be applied what can be in the worst case a spinlock (semaphore) in between the MCAL modules accessing the same hardware element from different cores. The performance impact of the exclusive area depends on the hardware element it shall be applied as well as the implementation of the spinlock. So for example hardware elements which are only written occasionally e.g. during start up or shutdown of the controller have a far less impact compared to "business" registers which are accessed frequently.

Figure 2.14: Separable Module on SW Level Example

An alternate solution to the protection of shared registers is to limit the access to one core only by finally changing the scope of the mappable element towards the next higher hardware element which allows an exclusive mapping to one core. Refer to Figure 2.13. For that purpose all accesses to the hardware element are coordinated by